High-Voltage Power Supplies Enhancing Production Line Stability in CMP

Stability in CMP production lines depends critically on eliminating sources of electrostatic chucking variability that manifest as wafer sliding, arcing events, non-uniform removal, or catastrophic dielectric puncture. High-voltage power systems engineered specifically for line stability incorporate multiple independent stabilization mechanisms that operate across timescales from nanoseconds to weeks.

At the fastest timescale, output ripple and noise must remain below a few hundred millivolts even during aggressive polishing head movements that modulate chuck capacitance. This requires active ripple cancellation circuits that inject counter-phase currents derived from continuous monitoring of the chuck-to-wafer gap impedance. Ultra-low ESR film capacitors placed physically close to the chuck feedthroughs, combined with multi-stage LC filtering, ensure that switching artifacts from the inverter stage never reach the wafer.

Medium-term stability addresses the challenge of slurry ionization and conductive film buildup on chuck surfaces over thousands of wafers. Advanced supplies implement periodic active discharge cycles that apply controlled bipolar waveforms to neutralize trapped charge in the dielectric while simultaneously measuring decay time constants. Deviations from baseline decay profiles trigger automated high-voltage conditioning sequences that restore surface resistivity without manual intervention.

Long-term stability relies on component derating and active health management. Critical high-voltage capacitors operate at less than 50% of rated voltage, while cooling systems maintain junction temperatures with ±1°C precision across ambient swings. Remaining useful life algorithms integrate voltage stress, temperature cycling, and partial discharge counts to schedule component refresh before parametric drift affects chucking performance.

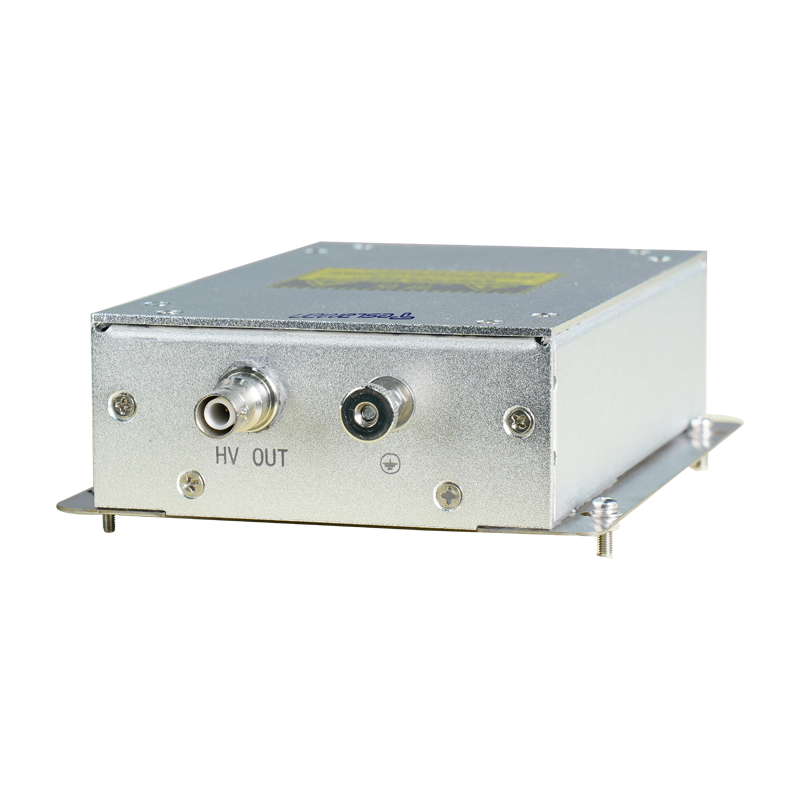

Redundant architecture plays a central role in eliminating single-point failures. Dual independent high-voltage generation paths with seamless transfer capability ensure that even complete failure of one channel results only in temporary reduction of maximum available chucking force rather than wafer loss. Automatic load sharing between channels prevents uneven aging while providing diagnostic separation of degradation sources.

Grounding and shielding strategies have evolved to combat electromagnetic coupling from adjacent tools in densely packed 300 mm lines. Optically isolated control signals and triple-shielded high-voltage cabling maintain common-mode rejection ratios exceeding 140 dB, preventing ground loops that could induce millivolt-level chucking force variations synchronized with neighboring equipment.

Real-time helium leak compensation represents another stability pillar. As backside helium flow stabilizes wafer temperature, minor leaks can alter effective dielectric constant and thus chucking force. High-voltage systems continuously measure the AC component of chuck current at diagnostic frequencies to infer gap changes and adjust DC voltage accordingly, maintaining constant electrostatic pressure within ±2% across the full range of permissible leak rates.

Arc-free operation during wafer placement and removal demands sophisticated pre-charge and de-chuck algorithms that shape voltage waveforms to follow the Paschen curve minimum. By approaching final voltage along optimized trajectories that avoid high-field low-pressure regimes, these systems achieve millions of transfer cycles without a single detectable arc event.

Integration with fab-wide voltage monitoring networks allows correlation of chucking anomalies with facility power events. Active power factor correction and ride-through capability exceeding 50 milliseconds protect against utility sags that would otherwise propagate as chucking force transients.

These combined measures routinely deliver month-long periods with zero chuck-related defects in volume production of advanced logic and memory devices, effectively removing electrostatic chucking from the Pareto chart of yield detractors.