Low-Noise Topology Optimization of High-Voltage Power Supplies for Electron Microscopes

The resolution of electron microscopes (EM) critically depends on the stability of high-voltage power supplies. Power supply noise causes electron beam trajectory deviation, leading to image blurring, loss of detail, or data distortion. Thus, low-noise topology optimization of high-voltage power supplies is central to enhancing EM performance.

1. Multidimensional Noise Analysis and Suppression Strategies

• Conducted Noise: Switching actions in power supplies generate high-frequency ripple (up to MHz), coupling to the electron gun via power lines. Multistage filtering (e.g., π-filters with LC combinations and common-mode chokes) suppresses differential and common-mode noise.

• Radiated Noise: Transformer leakage flux and PCB trace inductance emit electromagnetic radiation. Magnetic shielding (e.g., permalloy) around transformers and optimized switching frequencies (>200 kHz) reduce near-field radiation.

• Vibration-Induced Noise: Micro-vibrations in HV cables trigger triboelectric effects, generating μV-level noise. Low-noise coaxial cables (graphite-coated insulation) and secure bundling minimize charge accumulation.

2. Key Topology Optimization Technologies

• Multistage Conversion Architecture:

• PFC + LLC Resonance: Power Factor Correction (PFC) reduces grid harmonics, while LLC resonant converters enable soft-switching to minimize switching losses and noise.

• Post Linear Regulation: Linear regulators (e.g., LDOs) after DC-DC conversion suppress residual high-frequency noise, limiting output ripple to mV levels.

• Grounding Topology Innovations:

• Layered Star Grounding: Digital control, analog amplification, and HV output modules use separate grounds, converging at a single point to the chassis earth, eliminating ground loops.

• Ground Plane Segmentation: Split PCB inner layers into analog (AGND) and digital grounds (DGND) to isolate high-frequency digital noise.

• EMI Suppression Structures:

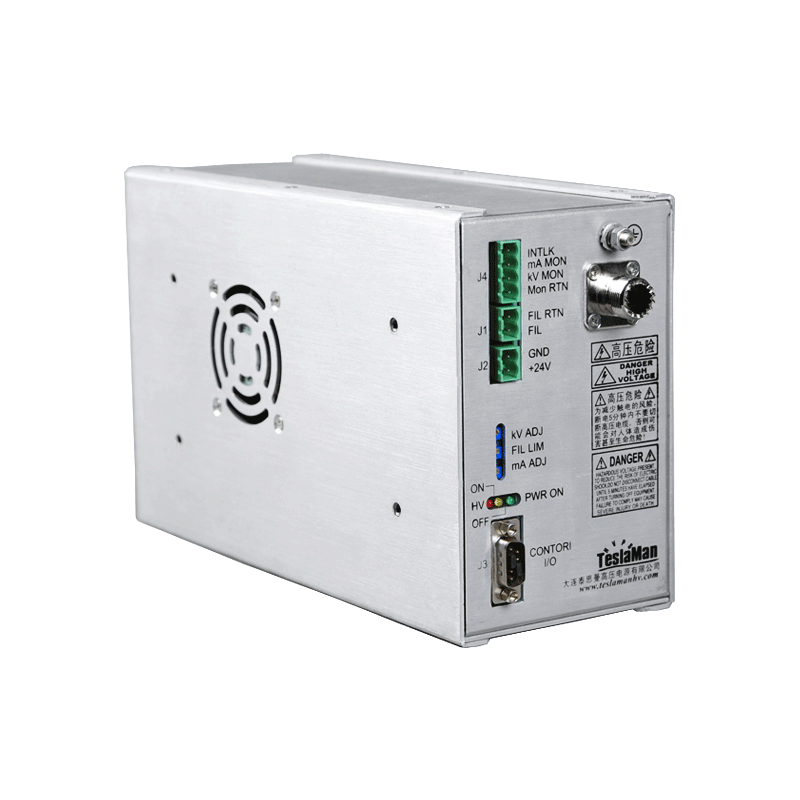

• Shielded Power Cavities: Enclose HV modules in isolated metal cavities with waveguide vents (apertures < λ/10) to block external RF interference.

3. Material and Layout Innovations

• Semiconductors: SiC MOSFETs replace silicon-based devices, reducing switching losses by 40% and minimizing reverse recovery current noise.

• Dielectrics: Polyimide films (dielectric constant 3.4, loss tangent 0.002) as transformer interlayer insulation lower capacitive coupling.

• Structural Layout: Maintain >15 mm horizontal spacing between HV and low-voltage circuits; place decoupling capacitors (10μF tantalum + 100nF ceramic) <5 mm from IC pins.

4. Testing and Future Trends

• Noise Evaluation Methods:

• Time-domain measurements (oscilloscopes + HV differential probes) capture μs-level transients.

• Frequency-domain analysis (spectrum analyzers + near-field probes) locate radiation hotspots above 30 MHz.

• Emerging Technologies:

• AI Dynamic Tuning: Predict noise spectra based on real-time load current, adaptively adjusting switching frequency and filtering parameters.

• Integrated Modular Design: 3D stacking of EMI filters, transformers, and regulators shortens return paths and reduces parasitic effects.