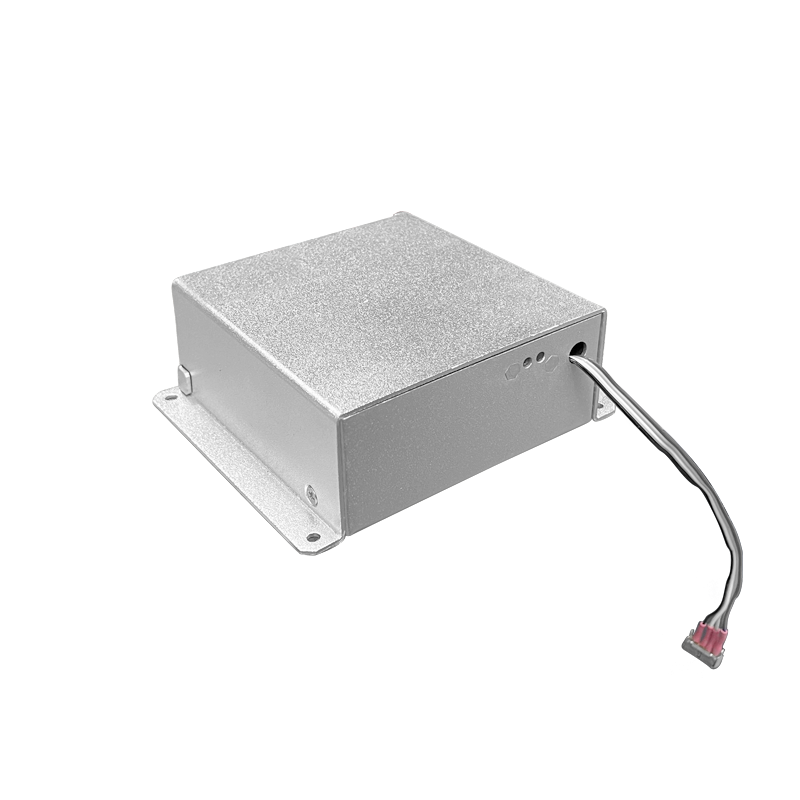

Single Event Effect Hardening for High-Voltage Power Supply in Lithography Machines

As the core equipment in semiconductor manufacturing, lithography machines require high-voltage power supplies (HVPS) to provide stable power with ±0.01% precision for electrostatic chucks (ESCs) and light source driving modules. However, Single Event Effects (SEE) — transient circuit disturbances caused by cosmic rays and high-energy particles — can lead to over 5% fluctuation in power output, directly resulting in lithography linewidth deviation exceeding 3nm and a sharp drop in chip yield.

SEE hardening requires a three-dimensional technical system: First, the circuit redundancy design adopts a dual-module hot backup architecture. A high-speed comparator monitors the output voltage in real time. When a Single Event Upset (SEU) is detected, the backup module switches within 0.8ms, ensuring the power supply interruption time is <100μs. Second, radiation-resistant silicon carbide (SiC) power devices are preferred for component selection. With a bandgap of 3.2eV, their Single Event Latch-up (SEL) threshold is increased to 120MeV·cm²/mg, which is 3 times higher than that of traditional silicon devices. Third, particle flux adaptive compensation is introduced at the algorithm level. A micro-semiconductor detector collects particle doses in real time (accuracy ±5%), and a PID neural network algorithm dynamically adjusts the output voltage, controlling the voltage deviation induced by single events within ±0.005%.

This hardening technology has been verified in the 7nm logic chip lithography process. After 1000 hours of particle environment simulation testing, the power output stability retention rate reaches 99.8%, and the chip lithography yield increases from 92% to 97.2%, effectively solving the SEE interference problem in high-precision lithography scenarios.